## 「先端パッケージング」生産基盤の確立が国内半導体産業復活のラストピースとなる

2026年2月17日

調査部 副主任研究員 梶田 真矢

### TSMCが熊本第二工場で3nmプロセスの先端半導体生産を表明

2026年2月、半導体受託製造最大手のTSMC（台湾積体電路製造：Taiwan Semiconductor Manufacturing Company）の魏会長は、高市首相と会談した。その中で魏会長は、当初計画を変更し、現在建設中の熊本第二工場で生産する半導体を3nmプロセス<sup>1</sup>の先端半導体とする方針を伝えた。3nmプロセスの半導体は、AIやデータセンター向けなどに利用される先端半導体である。

日本政府にとって、先端半導体を国内で自給し、国内企業に安定的に供給する体制を構築することは、経済安全保障の観点から重要な課題である。一方、TSMCとしては、需要が低迷している成熟プロセスの半導体<sup>2</sup>よりも、売れ筋である先端半導体の製造の方が投資効果が高いという経営判断があったと考えられる。また、供給網強化の観点から、台湾に集中している先端半導体の生産能力を米国や日本などに分散させ、最適化を図っていると推察される。

### 国内における先端半導体の生産基盤が整いつつある

加えて、米Micron Technology（Micron）が広島県で次世代半導体メモリ（DRAMおよびAI向けHBM：高帯域幅メモリ）の生産拠点を拡充している。また、キオクシアも三重県と岩手県で次世代半導体メモリ（NAND型フラッシュメモリ）の製造に向けた設備投資を行っている。さらに、北海道では、最先端となる2nmプロセスのロジック半導体の国産化を目指すRapidusが設立された。同社は、2027年度後半の量産化を目指し、準備を進めている。

このように、日本国内において最先端のロジックおよびメモリ半導体の生産基盤が整いつつあると言える（図表1）。

<sup>1</sup> プロセスノードやテクノロジーノードと呼ばれ、半導体の性能や製造技術を表す基準。数値が小さいほど性能が高いと言える。2026年2月時点で量産化されている最先端の半導体は2nmプロセスで製造されている。

<sup>2</sup> 当初計画は6～12nmプロセスの成熟半導体の製造を計画していた。

図表 1 国内における先端半導体（ロジック/メモリ）の生産基盤（計画含む）

| 企業名       | 生産拠点    | 生産品目                                                                  |

|-----------|---------|-----------------------------------------------------------------------|

| TSMC/JASM | 熊本県     | 第一工場：ロジック半導体（22/28nm・12/16nm）<br>第二工場：ロジック半導体（3nm）（当初計画では初回出荷2027年後半） |

| キオクシア     | 三重県、岩手県 | メモリ半導体（NAND型フラッシュメモリ）                                                 |

| Micron    | 広島県     | メモリ半導体（DRAM）（2026年から1γプロセス量産開始予定）                                     |

| Rapidus   | 北海道     | ロジック半導体（2nm未満）（2027年量産開始計画）                                           |

出所：経済産業省「半導体・デジタル産業戦略の進捗状況」や報道発表資料をもとに浜銀総研作成

## 半導体製造技術では、先端パッケージングが注目されている

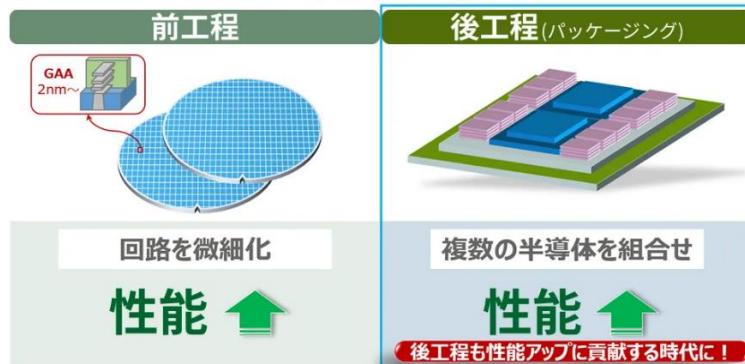

一方、半導体の製造技術では新たな潮流が見られる。それが、後工程<sup>3</sup>に属する「先端パッケージング」技術である。これまで、半導体は、回路の線幅を細かくする「微細化技術」によって性能向上が図られてきた。しかしながら、コスト高騰などを背景に微細化技術のみで性能向上を続けることは困難となりつつある。そこで、微細化とは異なるアプローチで半導体の性能向上を実現する技術「先端パッケージング」が注目されている。

先端パッケージングは、レゴブロックのように小片化された複数のチップを組み合わせる「チップレット技術<sup>4</sup>」など、半導体の後工程の技術によって性能を向上させる取り組みである。つまり、これまで単なる「組み立て」と位置付けられてきた後工程が、半導体の進化を左右する重要なカギを握るようになっていると言える。

図表 2 先端パッケージングのイメージ

後工程の技術で性能アップが必要な時代へ

出所：Rapidus Webサイト

<sup>3</sup> シリコンウェハーからチップを切り出し、チップと基板の接着、配線接続、封止などを行う組み立て工程をさす。対して、露光や現像、エッチング工程などシリコンウェハー上に電子回路を形成する工程は前工程と呼ばれる。

<sup>4</sup> チップレット技術の詳細は、HRIテーマレポート「[チップレット時代の神奈川県のポテンシャル -神奈川県が先端半導体の研究開発におけるオープンイノベーション拠点へ-](#)」において詳細に記載した。

冒頭で触れたTSMCは、「CoWoS」という独自の先端パッケージング技術を確立している。同技術はNVIDIAやAMD向けの高性能半導体に採用されている。そのほか、IntelやSamsung Electronics (Samsung) もそれぞれ独自の先端パッケージング技術の開発および採用を進めている。

この先端パッケージングでは、複数の半導体を組み合わせるための新たな製造工程が追加される。そのため、先端パッケージングによって、半導体製造装置および部素材分野で新たな需要が創出されると予測される。

## 先端パッケージングの国内生産基盤の不足が課題

ここで改めて、日本の半導体産業について考えてみる。TSMCやRapidusによって、日本は最先端クラスのロジック半導体の生産基盤を確保した。加えて、Micronによって最先端クラスのメモリ半導体 (DRAMおよびHBM) の生産基盤も整いつつある。また、先端パッケージングによって出現する新たな製造工程に必要な、半導体製造装置や部素材の技術も持っている。しかし、肝心の先端パッケージングの生産基盤は、どうだろうか？

TSMCは現在、台湾国内に先端パッケージングの拠点を持ち、今後米国においても同工程を行う計画である。日本国内でロジック半導体の製造が可能となったとはいえ、重要な先端パッケージング工程を海外に委託し続けるのでは、先端半導体の安定供給という目的を果たしているとは言い難い。日本における先端パッケージングの現状を確認すると、研究開発こそ進められているものの、量産化には時間がかかりそうだ（次頁図表3）。

図表 3 国内における先端パッケージングの主な取り組み

| 企業・団体名                 | 取り組み                                                                                                                                                                                                        |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JOINT2                 | レゾナックが中心となり設立した次世代パッケージング実装技術開発のコンソーシアム。半導体の装置、材料、基板メーカーが協業し、神奈川県川崎市の同社パッケージングソリューションセンターを拠点としている。2024年には同様のコンソーシアム「US-JOINT」を米国シリコンバレーに設立した。2025年には、パネルレベル有機インターユーザーに適した材料・装置・設計ツールの開発を加速する「JOINT3」が設立された。 |

| くまもと3D連携コンソーシアム        | 熊本地域の強みを活かし、基礎研究が行われているチップ積層型の三次元積層半導体について量産化に向けた技術開発を進めている。                                                                                                                                                |

| 自動車用先端SoC技術研究組合 (ASRA) | 種類の異なる半導体を組み合わせた自動車用SoCの研究開発を行い、2030年以降の自動車への量産適用を目指している。自動車メーカー、電装部品メーカー、半導体関連企業が参加している。                                                                                                                   |

| Rapidus                | 前工程と後工程を同じ敷地内で一気通貫で受託する構想を掲げている。大型パネルを利用した先端パッケージング技術の開発に取り組んでいる。                                                                                                                                           |

| Samsung                | 横浜市に異種チップ集積などの後工程の研究開発拠点「みなとみらいPackage」を設立。                                                                                                                                                                 |

| TSMC                   | 茨城県つくば市に三次元積層パッケージング技術の研究開発拠点を開設した。同社はそこで、部素材メーカー・半導体装置メーカーなどと連携して研究開発を推進している。                                                                                                                              |

| アオイ電子                  | 「FOLP (Fan-Out Laminate Package)」というチップレットなどの先端パッケージング技術を開発。シャープの三重工場を取得し、生産ラインを構築している。                                                                                                                     |

| ジャパンディスプレイ             | ディスプレイ技術を活用し、半導体パッケージング事業の拡大を図っている。                                                                                                                                                                         |

| レゾナック                  | 川崎市の研究開発拠点を中心に、次世代パッケージング実装技術開発のオープンイノベーションを推進している。                                                                                                                                                         |

出所：各社の報道資料などから浜銀総研作成

## 先端パッケージング基盤の整備が国内半導体産業復活のラストピース

日本メーカーは、半導体製造装置および主要な部素材分野において、高い技術力と世界的なシェアを有している。また日本国内では、最先端のロジックおよびメモリ半導体の生産基盤の整備も進んでいる。こうした状況においては、先端パッケージングを担うOSAT<sup>5</sup>の存在が、日本の半導体産業が復活を遂げるための欠かせない最後の要素（ラストピース）と言える。

現在、世界のOSAT市場は、台湾ASE Technology Holdingや米国Amkor Technologyといったグローバル企業が高い市場シェアを持ち、これらのOSATやTSMCが先端パッケージングの量産技術を有している。これに対して日本のOSATは規模が小さい。

<sup>5</sup> Outsourced Semiconductor Assembly and Test：半導体の後工程に特化した企業を指す。対して、NVIDIAなど半導体の設計に特化した企業をファウンドリ、TSMCなど半導体の前工程に特化した企業をファブレスと呼ぶ。

そのため、目下の先端パッケージを活用した先端半導体の供給体制構築の観点では、グローバルOSATの日本国内への誘致が有効な手段となるだろう。もっとも、これと並行して、日本型OSATの先端パッケージングモデルの確立が必要であると考える。例えば、日本が強みを持つ光電融合<sup>6</sup>チップやセンサーなどのアナログチップの異種混載への特化や、ディスプレイ技術を活用した大型ガラス基板を利用するパネルレベルパッケージング、半導体製造装置や部素材メーカーと連携した日本独自の先端パッケージングの技術の開発である。

今後、日本国内で製造されたチップをそのまま日本国内でパッケージングし、製品化まで完結させる「一気通貫型」の体制を構築するとともに、日本の強みを活かした先端パッケージング基盤を構築することが日本の半導体戦略の成否を分けると考える。

## 筆者紹介

袴田 真矢（はかまた しんや）

浜銀総合研究所 調査部 副主任研究員

半導体・電子デバイスなどテクノロジー領域の調査を担当

### 【本レポートについてのお問い合わせ先】

電話番号：045-225-2375

メールアドレス：[chitosabook@yokohama-ri.co.jp](mailto:chitosabook@yokohama-ri.co.jp)

### ＼ 調査レポートの更新情報を届けています ／

浜銀総合研究所では、景気動向や産業動向に関するレポートなどの発行情報をメールにてお知らせしています。ご関心のある方は、下記のサイトより、「レポート更新情報お知らせメール」（無料）にご登録ください。

【URL】 [https://www.yokohama-ri.co.jp/html/inquiry/inquiry\\_repo.html?nno=5](https://www.yokohama-ri.co.jp/html/inquiry/inquiry_repo.html?nno=5)

本レポートの目的は情報提供であり、売買の勧誘ではありません。本レポートに記載した内容は、レポート執筆時の情報に基づく浜銀総合研究所・調査部の見解であり、レポート発行後に予告なく変更することがあります。また、本レポートに記載されている情報は、浜銀総合研究所・調査部が信頼できると考える情報源に基づいたものですが、その正確性、完全性を保証するものではありません。ご利用に際しては、お客様ご自身の判断にてお取扱いいただきますようお願いいたします。

<sup>6</sup> 光信号と電気信号を統合する技術である。光は電気と比べ、低消費電力や高速通信、低発熱などの特性を持つため、膨大な消費電力や発熱という現在の先端半導体の問題に対する解決策として注目を集めている。